- ハードウェア

- CPU/メモリアーテクチャ

- 入出力装置

- リアルタイムOS(RTOS)

- ソフトウェアの開発

- 用語

- ベクトルプロセッサ

- MPU(Micro Processor Unit)

- Java EE(Java Platform,Enterprise Edition)

- EAI(Enterprise Application Integration)

- UDDI(Universal Description, Discovery, and Integration)

- エミュレータ

- シミュレータ

- プロファイラ

- SELinux(Security-Enhanced Linux)

- 周波数

- 周期

- ESD(Electrostatic Discharge:静電気破壊)

- クロック発生器(クロックジェネレータ)

- Hz(ヘルツ)

- 分周

- エネルギーハーベスティング

- 熱電変換素子

- 光起電力効果

- 焦電効果

- ピエゾ効果

- フールプルーフ

- フォールトトレランス

- JIS X 25010:2013

- イベントシステム

- マイクロカーネル

- インタフェース

- MVC(Model View Controller)

- C1カバレージ

- DC電源

- AC電源

- RAM、ROM

- DMA(Direct Memory Access)

- 方向レジスタ、データレジスタ

- シリアル通信

- ATPG(Automatic Test Pattern Generation)

- テストプローブ

- LSB(Least Significant Bit)、MSB(Most Significant Bit)

- スレッドとプロセス

- 割り込みと、ポーリング

- トランジスタ

- コンデンサ

- 暗号化方式

- MISRA-C

- Objective-C

- C99

- System C

- 加速時の距離を求める公式

- パワーゲーティング

- クロックゲーティング

- ターボブーストテクノロジ

- コンパイラ最適化

- SoC(System on a Chip)

- IPコア

- WebDAV

- スタックフレーム

- インサーキットエミュレータ

- 仮装デバイスドライバ

- ファジングテスト(fuzzing)

- 状態遷移テスト

- 特許の専用実施権

- 2の補数で負の数を表す

- Ah(アンペアアワー)

- リエントラント(再入可能)

- チップセレクト信号

- 限界値分析、同値分析

ハードウェア

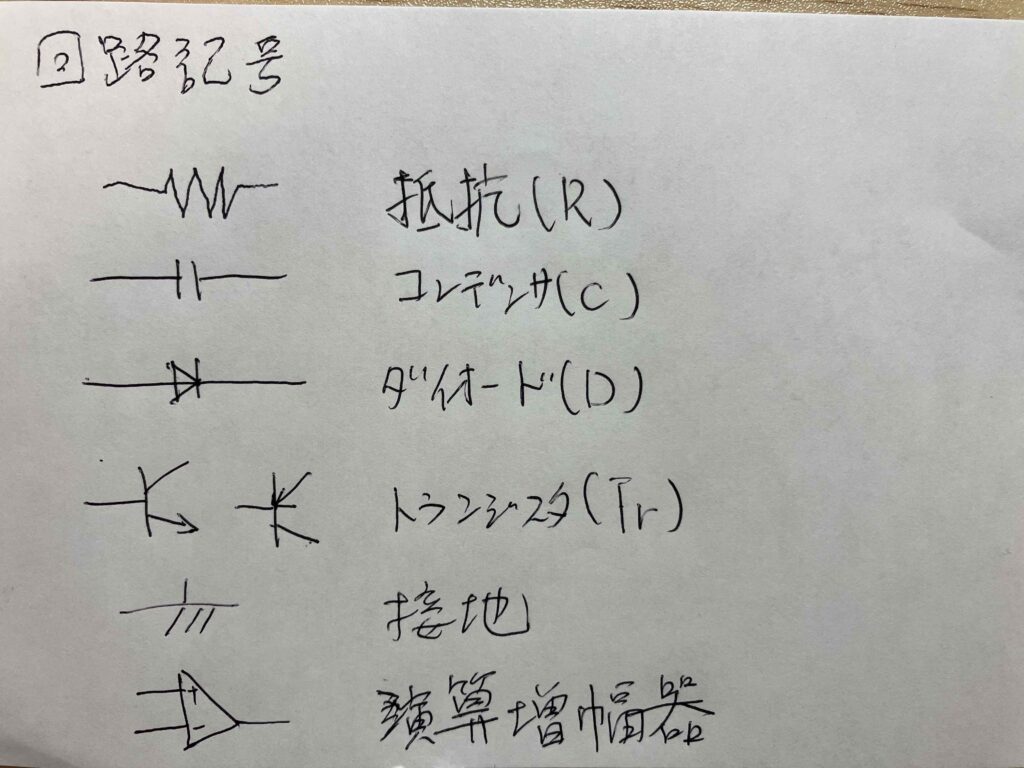

回路記号

論理回路

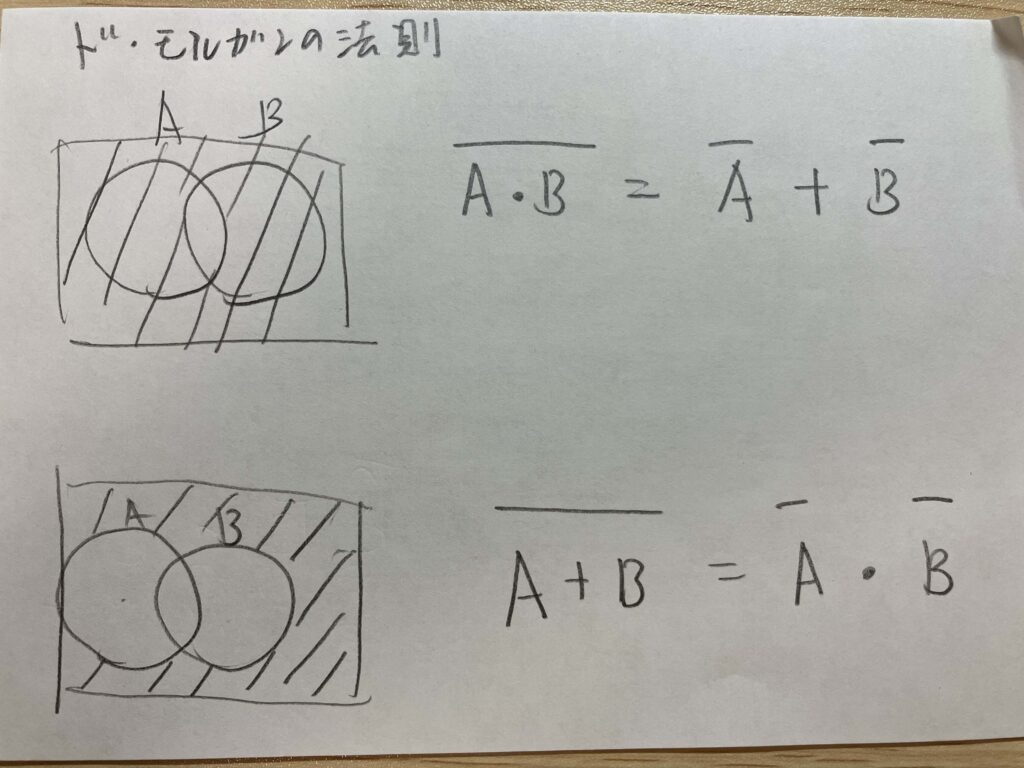

ド・モルガンの法則

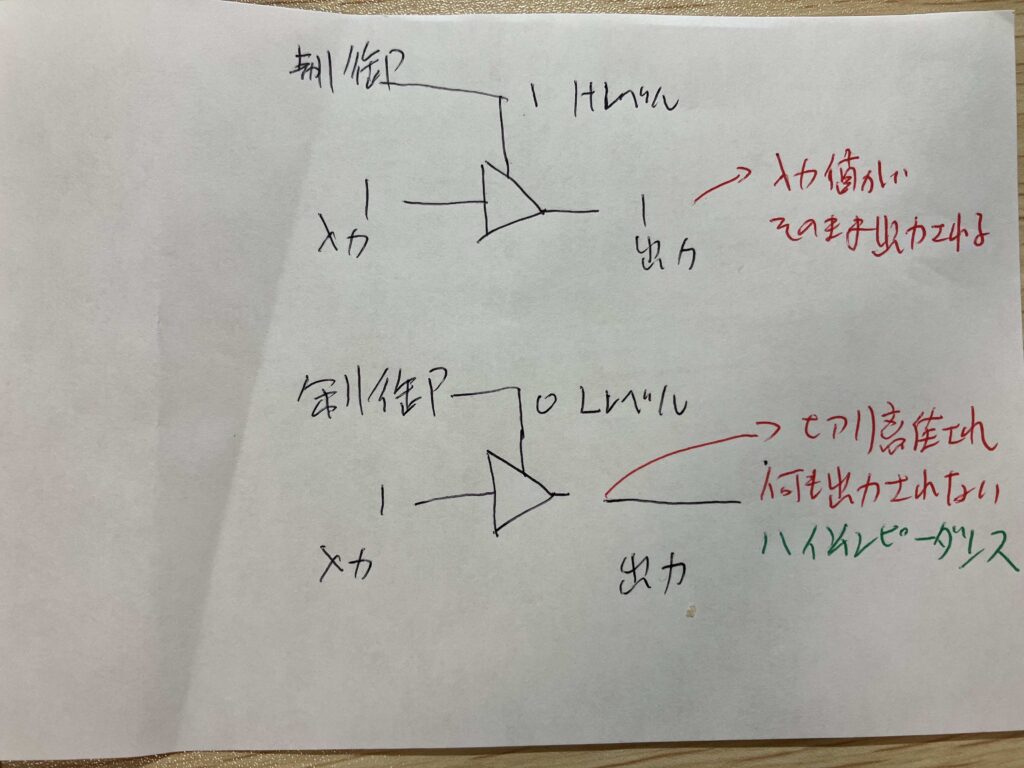

スリーステートバッファ

通常の論理素子は入力信号によって、「0」か「1」の状態となるが、一部の論理素子では0、1以外の状態ともう一つの状態をもつものがある。

スリーステートバッファは入力値ともう一つ制御信号をもつゲートがあり、ここが「0」の場合、出力は行われない状態(ハイインピーダンス状態)となる。

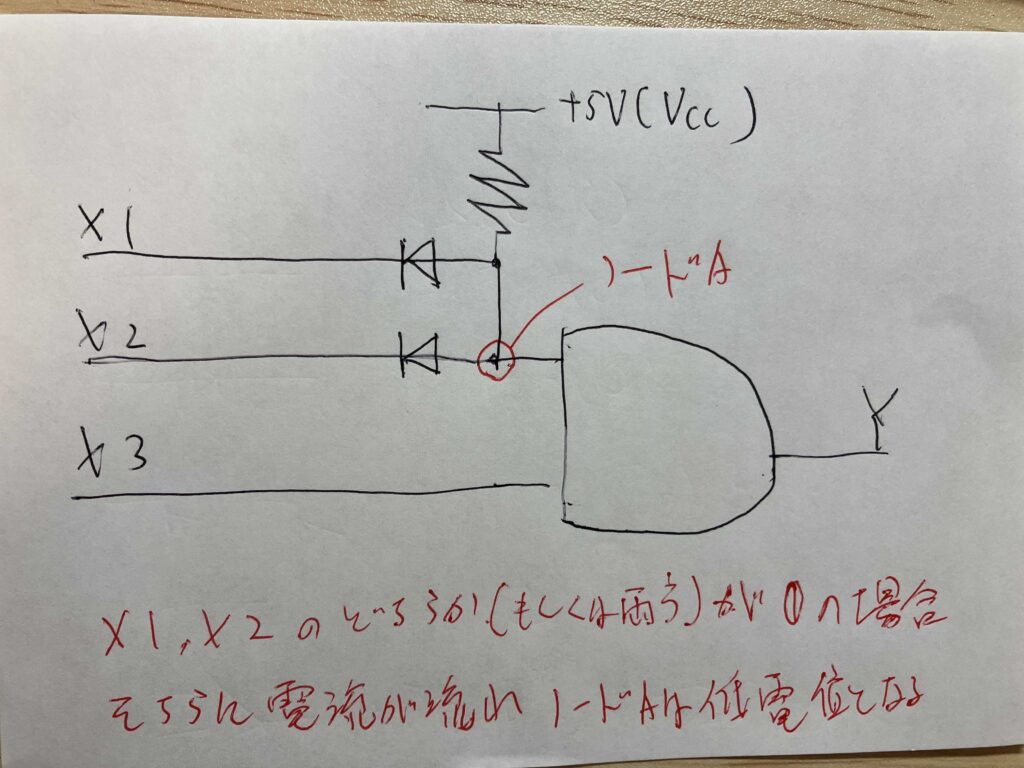

ダイオードと抵抗による入力の拡張

2入力ANDを3入力ANDにする回路

X1、X2いずれか(もしくは両方)が0の場合、そちらに電流が流れるため、ノードAは低電位となる。

X1、X2の両方が1の場合のみX方向に電流が流れず、ノードAが高電位(1)となる。

アナログ回路

カウンタ

カウンタは、保持している値を入力の立ち上がりまたは立ち下がりのタイミングで進める機能を持つ。

値の進め方によって2進カウンタ、10進カウンタ、グレイコードカウンタなどがある。

タイマ

あらかじめ定めた時間間隔で事象を発生させたい場合に用いられる。

カウンタのカウンタソースに周期的なクロックを入力することで形成される。

タイマ設定レジスタにタイマカウンタのカウント終了値を設定しておき、タイマカウンタはクロックの入力に同期してインクリメントされる。

比較機は常にタイマ設定レジスタとタイマカウンタの値を比較し、両者が一致したときに一致信号が出力され、タイマカウンタは初期化される。

ウォッチドッグタイマ(WDT:WatchDog Timer)

マイコン(MCU)のプログラムが暴走、停止していないかを監視するタイマ、MCUの動作を常に見張る「番犬」の役割を持つ。

マイコンは電子機器を制御する小型のコンピュータで、さまざまな電子機器に搭載されている。

これに異常があると電子機器が思わぬ動作をしてしまい、重大事故につながる可能性がある。

ローパスフィルタ

遮断周波数より低い周波数成分の信号のみを通過するフィルタのこと

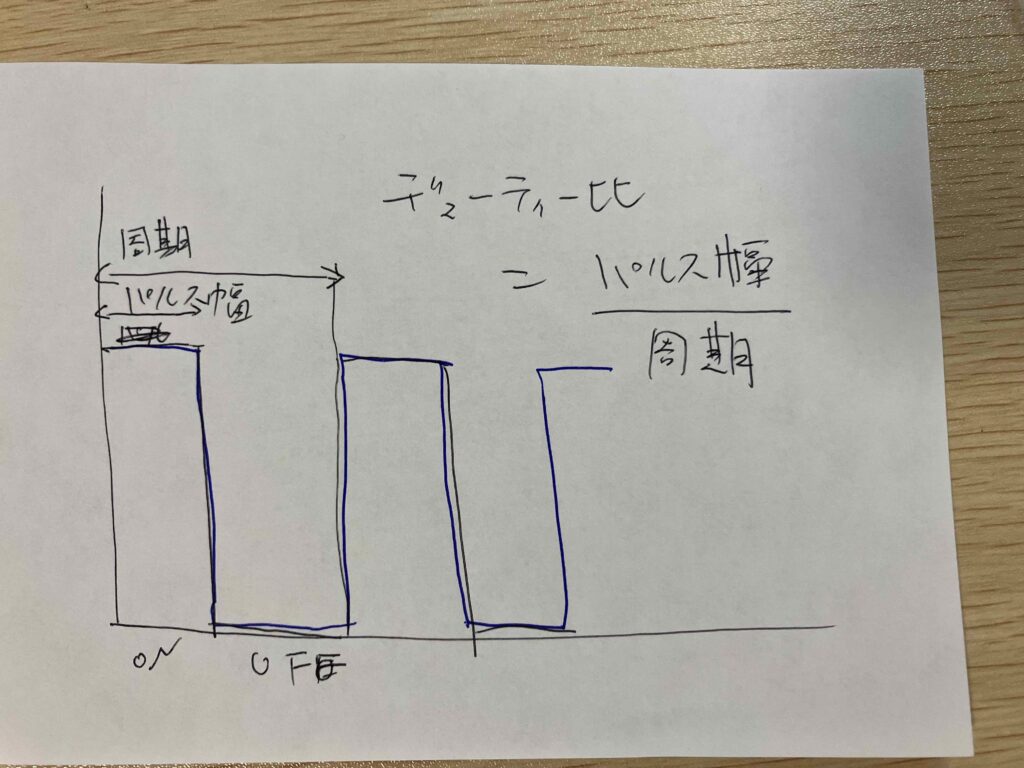

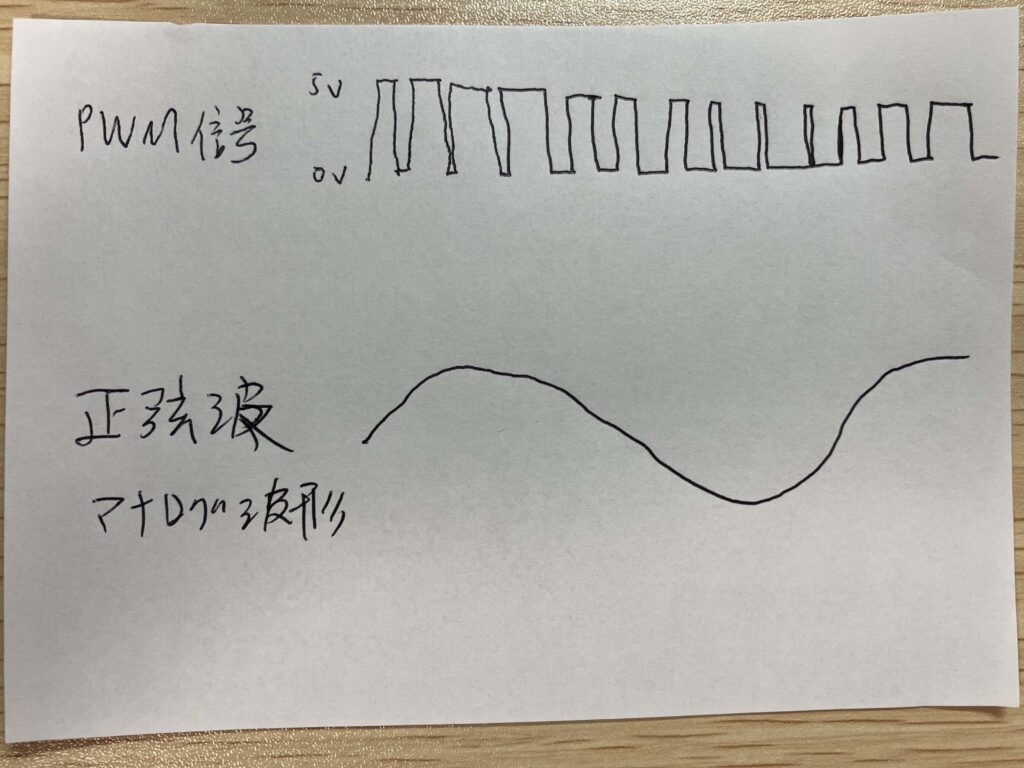

PWM(Pulse Width Modulation:パルス幅変調)

矩形波の周波数を一定に保ったまま、デューティ比(矩形波の1周期のうちHighが占める割合のこと)を変化させる方法である。

対応するアナログ値の大きいところに対応するパルス幅は広く、値の小さいところに対応するパルス幅は狭くすることによって表現する。

電圧が一定で良いので、MPUによる制御が容易となる。

デューティ比

PWMを用いたD/A変換回路

PWM信号をローパスフィルタに通すことでアナログ信号を得られる。

PWM信号は短波系であり、波形の立ち上がりと立ち下がりは高周波数成分が多くなり、ローパスフィルタでフィルタされ出力されない。(ローパスフィルタでギザギザをなめらかにするイメージ)

つまり、デューティー比が小さい部分はフィルタされる割合が高くなり電圧が下がり、デューティー比が大きい部分はあまりフィルタされず電圧が高くなる。

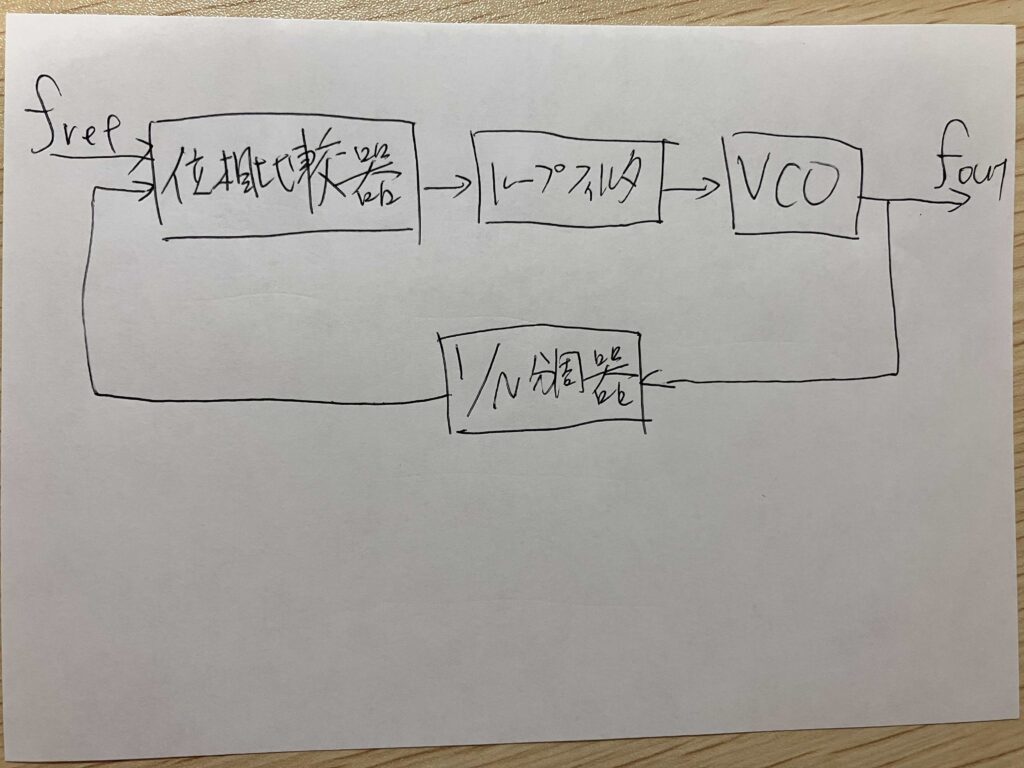

PLL(Phase Locked Loop:位相ロックループ)

PLLは入力された周波数を逓倍(整数倍すること)する回路である。

分周器の設定で出力周波数を変えることができるため、ソフトウェアで制御するのが容易

携帯電話など無線装置の周波数制御に用いられる他、高速クロックを用いるプロセッサ内部のクロック発生器にも用いられる。

出力周波数foutは基準周波数frefと分周器の分周比Nを用いて下記で表される。

fout=Nfref

位相比較器:入力された2つの信号の位相差を電圧に変換する回路

ループフィルタ:帰還のループフィルタとしてローパスフィルタを使う。無用な発振をフィルタする。

VCO:入力された電圧によって出力周波数を制御する。(電圧が高いと細かい波になる)

分周器:入力された周波数を整数分の1にして出力する回路

出力結果「fout」を1/Nに分周したものと、基準周波数「fref」が同じになるように調整されるため、「fref=1/N(fout)」となり、fout=Nrefとなる

位相比較器が位相のズレを検知→電圧が上がる→出力周波数が高くなる→その出力を1/Nしたもの(フィードバック)とFrefをもう一度比較

このページの解説がわかりやすい。https://kobaweb.ei.st.gunma-u.ac.jp/lecture/20190723_motozawa.pdf

D/A変換器

D/Aコンバータは、デジタル信号をアナログ信号に変換する回路のこと。

マイコンからスピーカーなどのアナログ入力が必要な部品を制御するのに使われる。

分解能がnビットのD/A変換器の場合、入力電圧は2のn乗で分割されるため、出力電圧は下記のようになる。

Vout=N✖️(Vref/2のn乗)

Vout:出力電圧

N:入力値

Vref:基準電圧(出力の最大値)

n:分解能

一般的な式で表すと下記になる。

出力値=(入力値/分割数)✖️基準電圧

入力値が最小値である0の場合出力値も0、入力値が最大値の2^nの場合出力値は基準電圧となる。

分解能

A/DコンバータやD/Aコンバータにおいて、測定対象となる信号(電圧)をどの程度細かく検出できるかを示す能力のこと。

分解能が10ビットの場合、VREF(正のリファレンス電圧)を2の10乗(1024)分割した精度でアナログ信号を取り出すことができる。

LSI(Large Scale Integration):大規模集積回路

トランジスタやダイオード、受動素子などを集積させて複雑な機能を実現する電子回路部品

フィールドプログラマブルロジック

ユーザ(システム設計者)が回路の機能を定義できるLSIのこと。

機能の記述、論理合成、配置配線の3ステップで進められる。

FPGA(Field Programable Gate Array)

「現場でプログラムできる論理回路の多数配列」の意味

通常LSIは製造後に回路構成を変更できないのに対し、ユーザーが設計現場でプログラムによって回路構成(処理内容)を変更できるのが特徴

設計フローとしては、FPGAが担う機能の記述を行い、その機能を実現するための論理回路の設計(論理合成)を行った後、論理回路用の配線を行うことになる。

FPGA設計実験の具体例

- パソコンを立ち上げ、開発用ソフトウェアを動作させFPGAの指定を含む開発環境の設定を行う

- ソースプログラムを書く

- コンパイル(論理合成)

- 入力ピンにどのスイッチを使うか、出力にどのLEDを使用するかを指定する(配置配線)

- もう一度コンパイルを行い、配置配線にミスがないことを確認

- 実験ボードの電源をONにし、FPGAに完成したプログラムをロードする。

- 動作を確認する。

SRAMベースFPGA

コンフィグレーションメモリにSRAMを用いたもの、SRAMは揮発性のため電源をOFFにすると情報が失われる。

そのため、コンフィフィグレーションデータ(設定情報のプログラム)をFGPAとは別に用意した不揮発性メモリに格納しておき、電源ON時にSRAMコンフィグレーションメモリにロードされる。

高い集積度と高い性能が特徴、消費電力は大きくなる。

アンチヒューズFGPA

書き込み電圧を加えると接続状態になるヒューズの逆特性の素子を使用したFGPA(普通のヒューズは電圧を加えると絶縁状態になる)、書き込みは一度しか行えない。

メモリ

SRAM(Static Random Access Memory)

複数のトランジスタで構成されたフリップロップ回路を使用した揮発性メモリである。

通電中はリフレッシュを行わなくてもデータを消失しない。読み書き速度が早く消費電力が少ないが高価である。

CPUなどのキャッシュメモリにはSRAMが使われる。

DRAM(Dynamic Random Access Memory)

コンデンサとトランジスタで構成される揮発性メモリであり、コンデンサに蓄積された電荷でデータを記録する。

時間と共に電荷が失われるので、データ保持のために定期的な書き直し(リフレッシュ)が必要

リフレッシュ周期の計算

DRAMはチップ上に形成した微小なコンデンサに電化を蓄えることでデータを保持しており、時間と共に電化が失われるのでデータ保持のために定期的なアクセスを行う必要がある。

アドレス線が10本で、1Mワードの容量を持つDRAM、リフレッシュのために全てのROWアドレスを51.2msの間に1回更新する場合

1Mワードということは1,048,576ビット(2の20乗)個のワードを持つ、本来なら20本のアドレス線が必要だが、1本のアドレス線でROWアドレスと、Columnアドレスの2回に時分割して、ワードアドレスを指定することで半分の10本で済む。

10本のアドレス線で指定するROWアドレスは2の10乗で1,024個ある。

リフレッシュは全ROWアドレスを51.2m秒の間に1回更新とのことなので、51.2を2の10乗(1,024)で割ればよい。

51.2➗2の10乗 = 51.2➗1024=0.05ms(50マイクロ秒)

ReRAM(Resistive RAM)

電圧を加えると電気抵抗が変化する金属酸化物阻止を利用した不揮発性メモリである。

フラッシュメモリ

不揮発性の半導体メモリで、安価に大容量化できることが特徴

システムに組み込んだ後でも内容の変更が容易

書き換え可能回数に制限があり、長期間書き込みを行わないとデータが消失する可能性がある。

動作原理はこちらのページがわかりやすい。(https://semi-journal.jp/basics/device/memory/flash.html)

NOR型

配線が並列でそれぞれのメモリセルにソース線を配線する必要がある。

バイト単位のランダムアクセスで読み出し可能

小容量、書き込みが遅い、保存したデータは基本壊れない。

ファームウェアの格納用として用いられる。

NAND型

メモリセルを直列に接続し、ソース線を複数のメモリセルで共有できるため高集積化が可能

ブロック単位(数kバイト)のシーケンシャルアクセスで読み出し可能

大容量、書き込み速度が速いがデータの信頼性が低いため、エラー訂正を行うコントローラーが必要

情報を保存する素子であるメモリセルに記録する情報量によってSLC(Single-Level Cell)とMLC(Multi-Level Cell)の2種類に分けられる。

SLCは1ビットの情報(0、1)を1つのメモリセルに保存するのに対して、MLCは2ビット以上の情報(00、01、10、11など)を1つのメモリセルに保存できるため記憶効率が良くコストも安い、ただしSLCに比べ劣化が早く寿命が短いというデメリットがある。

SLCはサーバーなどの産業用に、MLCはコンシューマ製品に利用されることが多い。

CPU/メモリアーテクチャ

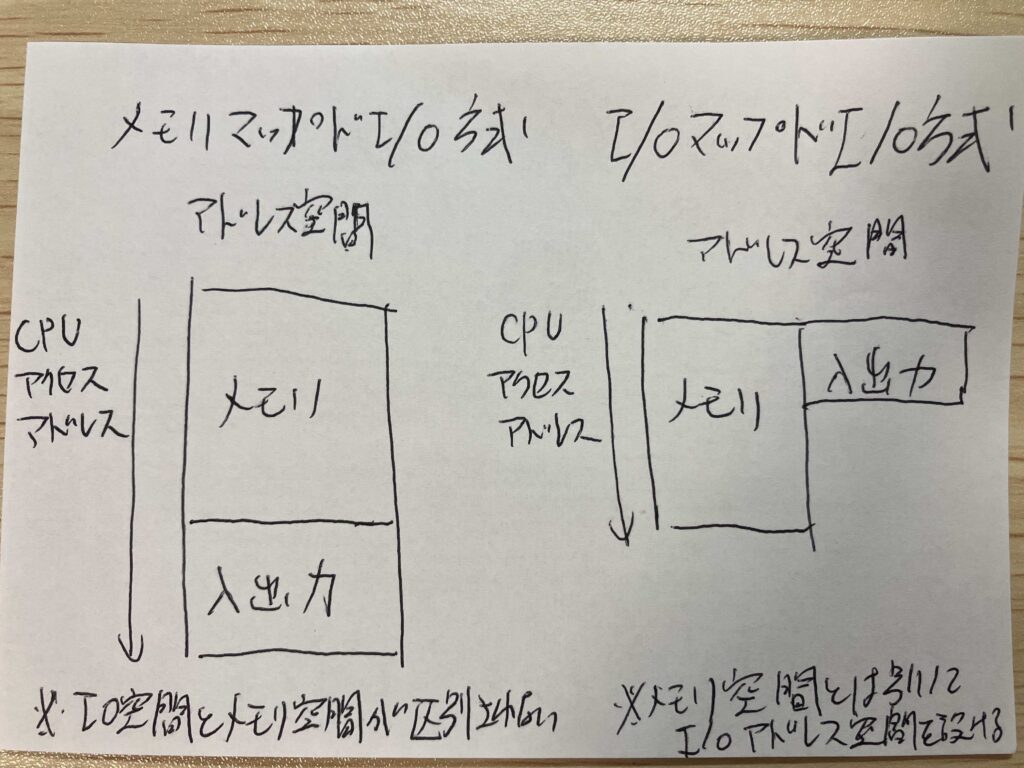

I/Oアクセス方式

メモリマップドI/O方式

CPUがI/O(入出力)デバイスにアクセスするための命令を、メインメモリにアクセスするための命令と同じアドレス空間で扱う方式のこと。

入出力機器はCPUのバスを監視し、自身のレジスタがマッピングされた空間へのCPUからのアクセスに応答する。

利点:CPUのアドレス空間をメインメモリと共有することによって、I/Oデバイスとメインメモリを同じ命令で扱うことができ、アドレス空間の自由度が大きくなる。

欠点:CPUとI/Oデバイスが同じメモリアドレスを共有することになり、プログラミング上、注意が必要な場合がある。

CPUがキャッシュ機能を持っている場合、I/O空間のデータ内容が変化してもこれを検出できないことがある。

例えば、I/Oデバイスの状態がある番地にフラグとして書き込まれる場合、プログラムではそのフラグを繰り返し読み込む必要がある。

このプログラムをC言語で書き、最適化オプションを有効にしたまま、ループでフラグを何度も読み込むと2回目のアクセスからフラグの内容をレジスタに格納してそちらを読み込んでしまう。

対策としてはvolatile型就職誌をつけて宣言する。(volatileの訳は「揮発性」)これによってレジスタによる最適化を行わせないようにできる。

I/OマップドI/O方式

CPUがI/O(入出力)デバイスにアクセスするための命令を、メインメモリにアクセスするための命令と別のアドレス空間によって扱う方式のこと。

利点:メモリのアドレス空間を無駄なく利用できる。

欠点:ハードウェア(レジスタなど)が必須となる。

現在はメモリ容量が大きく、メモリの一部をI/Oに使ってもメモリの使用上困らない。

メモリアーキテクチャ

メインメモリの制御

ページ置き換えアルゴリズム

LFU方式(Least Frequently Used)

新たにデータを格納する際、利用頻度の低いデータから順に置き換える方式

LRU方式(Least Recently Used)

新たにデータを格納する際、最も長い間アクセスされなかったデータから順に置き換える方式

直近の利用頻度が反映されるため最もヒット率が高いとされている。

FIFO方式(First In First Out)

新たにデータを格納する際、登録が最も古いデータから順に置き換える方式

登録の古いものは利用頻度も下がっているという過程に基づいている。

LIFO方式(Last In First Out)

登録の新しいデータから順に取り出す方式

プロセッサの処理においてレジスタ及びメモリの内容を退避するためのスタック制御に利用されている。

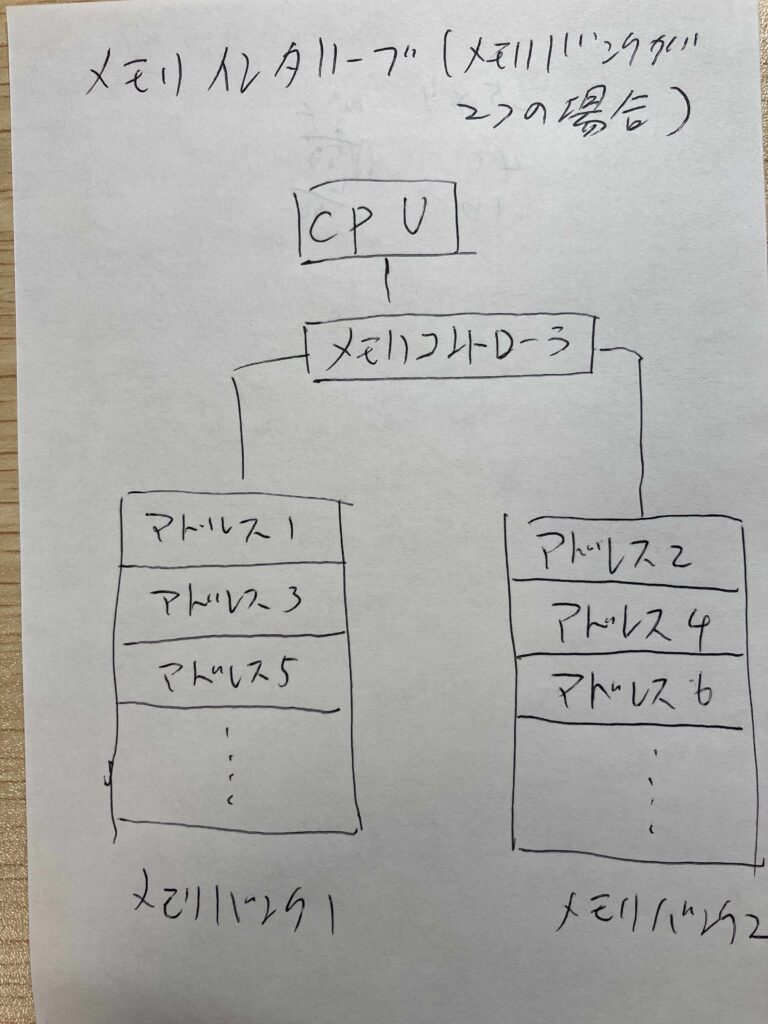

メモリインタリーブ

主記憶の高速化技術の一つ

主記憶を複数のバンクに分け並列的にアクセスすることでアクセスを高速化する技術

主記憶はCPUより低速なため、複数のメモリバンクに並列的にアクセスすることでCPUが連続したアドレスに対してアクセスした場合の転送レートを上げることができる。

キャッシュメモリ

キャッシュメモリは、メインメモリとCPUとの間に配置される高速メモリのこと。

メインメモリがボトルネックとなってCPUが本来の性能を活かせないことを防ぐ。

キャッシュの制御方式

ライトスルー方

書き込み時にキャッシュ上にデータがあるかないかにかかわらず、主記憶に書き込む方式

キャッシュメモリと主記憶の不一致は発生しないが、主記憶へのアクセス回数が増えるという問題が起こる。

ライトバック方式

キャッシュ上にデータがある場合には、キャッシュだけに書き込み、主記憶へはキャッシュのページの入れ替えなど、必要となった時に書き込む方式

キャッシュメモリと主記憶の不一致が発生することがあり、DMAで主記憶の誤ったデータを読み出される問題が発生する可能性がある。

これをコヒーレンシ(一貫性)問題といい、バススヌープとディレクトリ方式の2つの対応策がある。

バススヌープ

スヌープ(snoop)は「覗き見る」という意味

バス上でやり取りされる全てのデータを監視し、主記憶に未反映の可能性がある領域へのアクセスを検出する。

主記憶にキャッシュメモリの内容が未反映のエリアに対してDMAが読み出しを行おうとした時は、そのアクセスが無効であることを示す信号を出し、読み出しを一時停止させる。

その後、キャッシュ上のデータを主記憶に書き出した上で読み出しを再開させる。

ディレクトリ方式

キャッシュとして保有しているメモリブロックを主記憶上で管理する方式

メモリやバスを共有しないマルチプロセッサシステムで使用される。

CPU高速化アーキテクチャ

パイプライン制御

パイプライン制御はプロセッサの処理を、フェッチ、デコード、実行、メモリなど複数の処理ステージに細分化して、複数の命令を並列に実行することを特徴とする高速化手法

パイプラインは石油が次々とパイプを通過して流れていくパイプラインと動作が似ていることに由来する。工場の生産工程で見られる流れ作業も同じ概念である。

命令に要する時間=(D+I-1)✖️P

D:パイプラインの深さ

I:命令スロット数

P:パイプラインのピッチ(秒)

パイプラインバブル

パイプラインで分岐命令があるとパイプライン上に残っている実行中の命令を破棄しなければならず、スループットが下がる。これをパイプラインバブルと呼ぶ。

パイプラインバブルを避けるには投機実行と、遅延分岐がある。

投機実行:あらかじめプログラムの分岐先を先読みして実行する手法、予測の精度が高ければスループットが上がる。

遅延分岐:先に実行しても問題のない命令を分岐の前に実行する。分岐を遅延させる。

スーパーパイプライン

パイプラインの処理ステージをさらに細分化したもの。

通常のパイプラインが5段階程度なのに対し、スーパーパイプラインは10段階以上の工程に分類される。

並列実行する命令数が増えてスループットが上がるが、分岐命令が発生したときのペナルティが大きい。

(例)F、D、E、M、W→F1、F2、D1、D2、D3、D4…

スーパースカラ

スーパースカラはパイプラインを複数用意し、同時に複数の命令を実行できるようにしたものである。(パイプラインが複数あるので同じ工程を同時に実行できる)

スカラ(scalar)はベクトルを持たず、大きさのみで表す量のこと。

プログラム中に前後の命令の影響を受けずに独立して実行可能な命令があるとき、ハードウェアでこれを検出し、複数のパイプラインに処理を割り振って並列実行させることで高速化を実現する。

プログラムによっては処理の順番を入れ替えることでCPUの処理に最適になるように並べ替えることが可能な場合があり、これをアウトオブオーダー実行という。

VLIW(Very Long Instruction Word)

直訳すると「とても長い命令語」

複数の命令をまとめて一つの命令としてまとめて同時に実行する方式

通常のパイプライン処理では命令の依存関係をCPUが判断しながら実行するが、VLIWではあらかじめ依存関係のない命令となっているのでCPUの構造を単純化できる。

ソースコードからプログラムを作成するコンパイラの設計が難しくなるという欠点がある。

パイプラインハザード

分岐命令以外にも、パイプラインの流れを阻害する要因がいくつかある。これらをパイプラインハザードと呼ぶ。

データハザード

直前の命令の実行結果を、次の命令が使用する場合、次の命令は直前の命令の結果が受け取れるようになるまで待たなければならない。

このようにして待ちが発生することをストールという。

構造ハザード

複数の命令スロットが、一つしかないCPU内部の資源を同時に利用しようとしたために発生するハザードのこと。

制御ハザード

分岐命令によるハザードの事。

割り込み制御

実行中のプログラムを一時的に止めて別の処理を優先的に行わせるために利用される。

割り込みオーバーヘッドにより処理負荷が上がる可能性があるため、設計時には発生頻度に注意する必要がある。

外部割り込み

プログラムの実行とは無関係に、ハードウェアの状態によって発生する割り込み

(例)

- 入出力完了

- 所要時間の経過

- 電源電圧の低下

内部割り込み

CPU自体が発生させる割り込みのこと。

(例)

- 0除算:演算め入れで0で除算しようとしたとき

- オーバーフロー:演算の結果、桁あふれが発生したとき

- 書き込み禁止領域への書き込み:あらかじめ定められた範囲以外のアドレス領域へアクセスしようとした場合

- 割り込み命令による割り込み:割り込みを発生させる命令が実行されたとき

NMI(Non-Maskable Interrupt)

致命的な問題が起きた場合に発生する割り込みのこと。

割り込みの大半はソフトウェアによって禁止/許可の設定が可能であるが、NMIについては設定できない。

(例)

- ウォッチドッグタイマがタイムアウトしシステムをリセットする処理を行う場合

- 電源電圧の低下によりシステムの誤動作が懸念されるため、シャットダウンを行う場合

入出力装置

エンコーダ

物体の位置などを検出し、その結果をディジタル符号として出力するハードウェアをエンコーダという。

回転方向の変異を測定するものをロータリエンコーダ、直線方向の変異を測定するものをリニアエンコーダと呼ぶ。

一般には、あらかじめ決められた規則に基づいてデータを符号化するソフトウェアを「エンコーダ」という。例えば、データ圧縮アルゴリズムを用いて画像や音声データを圧縮するものがある。

ロータリエンコーダ

モータなどの回転軸に固定されたスリット円盤を利用してパルス(ディジタル信号)を出力し回転角を検知するものをロータリエンコーダという。

ロータリエンコーダは、出力するデータの種類により、インクリメンタルエンコーダとアブソリュートエンコーダに分類される。

インクリメンタル方は相対的な回転位置と方向を検知し、アブソリュート型はスリット円板の各位置から異なる信号が出るようにして絶対的な回転位置と方向を検知する。

インクリメンタルエンコーダ

機械的な位置の変化量をディジタル値で出力する。

回転するスリット円盤と固定スリット円板の間を光が通過する際、パルスの数をカウントすることによって回転速度が得られる。

固定スリットはスリット円盤に入射する光の幅を規制し、スリット円盤の回転によって光のON/OFFが明確に行われるようにする。

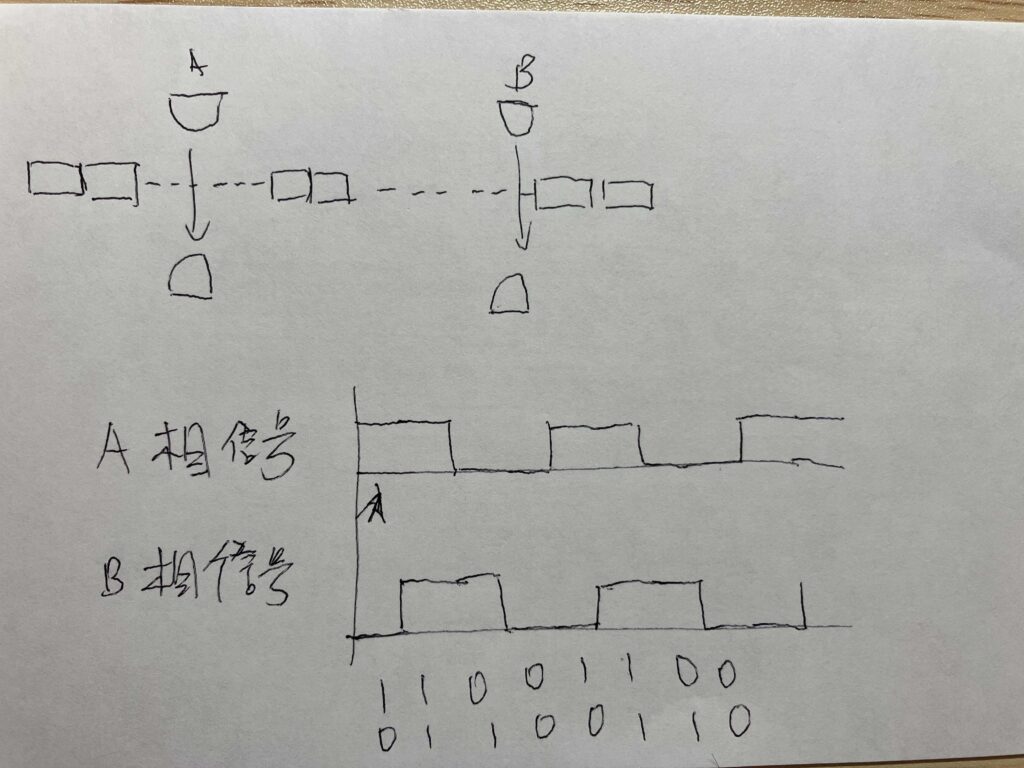

2相クロックエンコーダ

2相クロックエンコーダはインクリメンタルエンコーダの一種であり、位相が1/4ずつずれたA相及びB相の2組の出力を持つ。

2組の位相の波形パターンによって回転方向を知ることができる。

両者の相違差は1/4であるため、1パルスの出力周期中には、A相、B相の出力の組み合わせとして、4通りの状態が存在する。

従って、角度分解能は1パルスに相当する角度を4等分した角度に等しい。

1回転で90パルスの出力が行われる2相クロックエンコーダでは、1パルスに対応する角度は

360÷90パルス=4度/パルス

であるから、角度分解能は、下記となる。

4度÷4状態=1度

インタフェース技術

シリアルインタフェース

データを1ビットずつ順に送る方式のインタフェース

データ信号線は1本であるため、制御信号線が別にあっても全体の信号線の数を少なくできるというメリットがある。

パラレルインタフェース

複数ビットのデータ用信号線と通信制御用の信号線とを用いてデータの受渡しををする方式

代表的な規格として、プリンタ用のパラレルポートSCSI(Small Computer System Interface)インタフェース、IEEE 488などがある。

高速化を実施すると、データの各ビット間での信号到達タイミングの整合をとることが困難になる。

高速シリアルインタフェース

クロック信号を用いた同期が困難なため、データの信号に「0」「1」が長く連続して出現しないように冗長化して伝送するエンベデッドクロックの技術が利用されている。

冗長化の規格には8b/10b符号化や、64b/66b符号化、128b/138b符号化などがある。

受信側ではデータの信号から同期タイミングを抽出してデータを再現する。(クロックリカバリ、クロックデータリカバリ)

8b/10b符号化

8ビットのデータを10ビットのシンボルに変換して伝送する方式

データは変換テーブルによって変換されるが、信号がHigh(Low)となる連続する期間が4クロック以下となるようになっている。

8ビットのデータを10ビットで送るので伝送効率は80%になる。

USB(Universal Serial Bus)

パソコンと周辺機器を接続するためのインタフェースとして、主にパソコン関連のメーカが中心となって制定した規格

ホストコントローラを中心としてツリー状に最大128台までの機器を接続することができる。

電源供給機能、ホットプラグ(機器の電源を入れたまま抜き差し可能)、アイソクロノス転送(相手からの受信確認を行わずに決まったタイミングでデータを送信し続ける)といった特徴がある。

1番ピン:VBUS(5Vの電源)、2番ピン:ーData、3番ピン:+Data、4番ピン:GNDとなっている。

シリアルATA(SATA)

ハードディスクなどの記憶装置を接続する規格であるATA仕様の転送方式を、従来のパラレル型からシリアル方式に変更したもの。

従来のパラレル方式での伝送方式が133Mバイト/秒だったのに対し、STATは155⇨300⇨600Mバイト/秒と高速化が行われた。

表示装置

GND(グランド)

回路内の基準となる電位との差が「0ボルト」になる部分のこと。すなわち回路内の電圧の基準を決める部分

発光ダイオード(LED)

LED(Light Emitting Diode)は電流を流すと発光する半導体素子

アノード(正極)とカソード(不極)をもちこの間に数ボルトの電圧をかけることで発光する。

電流の向きは正しい向きが決まっており、反対に取り付けると光らない。

アノードコモンとカソードコモン

LEDのプラス側をアノード、マイナス側をカソードと呼ぶ。

端子数や配線数を減らす目的で、アノードもしくはカソードを共通にすることをアノードコモン(カソードコモン)と呼ぶ。

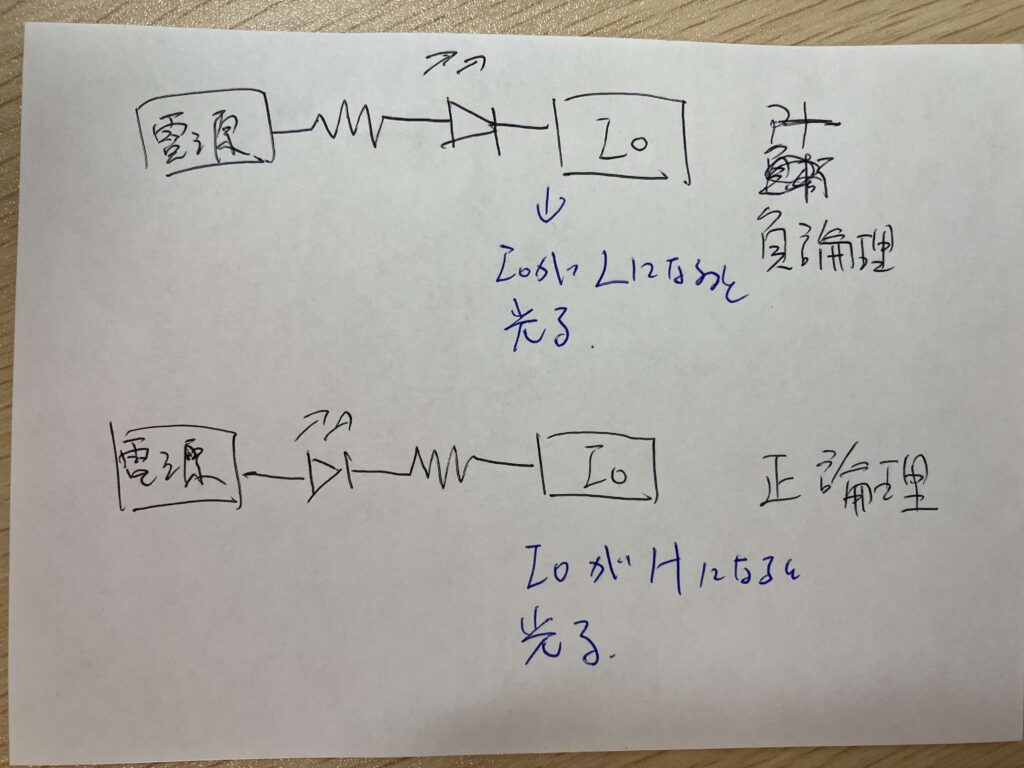

正論理で接続、負論理で接続

無線インタフェース

ZigBee

センサーネットワーク向けに策定された低速・低消費電力の無線通信プロトコル。

Zigzag(ジグザグ)に飛び回り、巣に帰って仲間に情報を伝達するBee(ミツバチ)の生態にちなんだ名称

周波数は868MHz帯、915MHz帯、2.4GHz帯のいずれかを用いる。

同じ周波数帯を用いるBluetoothと比較して通信速度は低速であるが、同時接続数が多く、通信距離が長いことが特徴

乾電池のような小型の電源による長時間の動作を可能にする技術で、非常に小さな機器に組み込むことができる。

Bluetooth

携帯電話などのモバイル端末とヘッドセットなどの周辺機器と接続するための近距離無線として使われる。

Bluetooth4.0から大幅に低消費電力化されており、一部ZigBeeとは用途によって一部競合する。

IrDA(Infrared Data Association:赤外線データ協会)

赤外線データ協会が決めた赤外線の規格

赤外線を利用して実現される無線通信であり、テレビ、エアコンなどのリモコンに使われる。

なお、リモコンは一般的に独自規格による赤外線を利用した無線通信を行なっている。IrDAに対応した機器であればスマホなどでエミュレートすることも可能

モータ

DCモータ(直流モータ)

直流電圧を印加することで、回転運動が得られるモータのこと。

回転数の制御には、印加する電圧を用いる方法(リニア制御)とPWMによる方法がある。

モータ内に永久磁石があり、そこに直角の角度でコイルを配置し電流を流すとフレミング左手の法則に従い、上下方向に電磁力が発生する。

コイルが90度回転するとブラシが接触しなくなり電流が止まるが、コイルは惰性で回転を続ける。再び電流が流れると同じ方向に回転を繰り返す。

ACモータ(交流モータ)

内部にブラシなどの機械的な接点を持たず、交流電流を入力することで駆動するモータのこと。

誘導電流によって駆動する。

複数のコイルが配置されたステータとその内部にロータを配置する。

コイルに電流が流れることで、ロータに誘導電流が発生する。

ステータ内のN極、S極が交流電流によって変化するので、ロータに流れる電流の向きも変化し、フレミング左手の法則によってロータも回転する。

コイルを上下に配置すると、N極、S極が反転するだけでうまく回転しないので、90度の位置にも配置し、位相をずらすことで、うまく回転するようになる。

サーボモータ

サーボの語源は「Servant:召使い」

決められた位置、速度、回転力(トルク)で正確に動いてくれる。

電磁石をN極、S極に変化させて、永久磁石を引きつけたり引き離したりしてモータを回転させる。

回転センサである「エンコーダ」が付いている。

エンコーダにはスリットが固定された円盤、光センサがあり、動いたスリットをカウントして、回転時の位置や速度を検出できる。

司令塔であるサーボコントローラーがモーターを動かすサーボアンプに指令を与え、サーボアンプが駆動部に電力を供給する。

サーボアンプはエンコーダからフィードバックを受け取り、コントローラからの指令と、誤差が0になるようにサーボモータの出力をコントロールする。

スイッチ

マトリクススイッチ

多数のスイッチを接続する場合に、入出力ポートおよび配線を有効活用するために用いられる接続方法およびその制御方法

M✖️N個のスイッチを単純にポートに接続すると、M✖️N個の入力ポートが必要となるが、ポート数を節約したいときに、M本の出力ポートと、N本の入力ポートで済ませる方法

行方向の入力ポートから時間で区切って信号を出す、出力ポートのどのポートにきたかを検知して、入力ポート、出力ポートがそれぞれわかるので、どのスイッチが押されたかわかる。

リアルタイムOS(RTOS)

タスク管理

プリエンプティブ方式

preemptは「先取する」の意味

優先度のより高いタスクが起動すると、現在実行しているタスクの実行権を横取りして動作させることを特徴とすタスク制御方式。

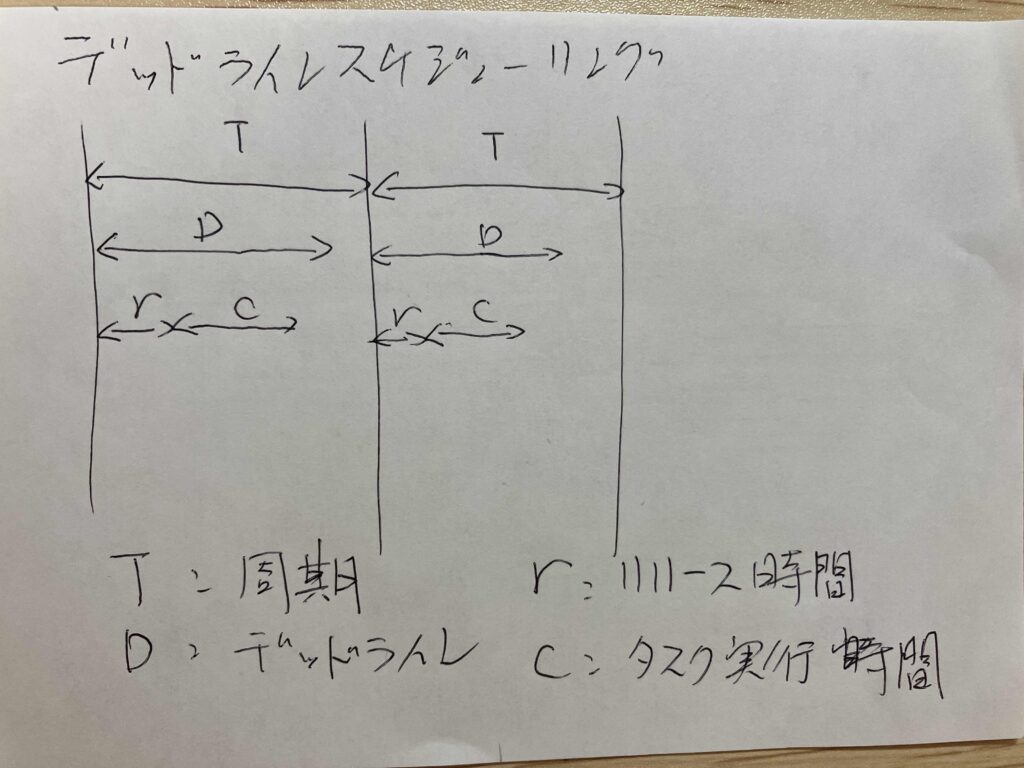

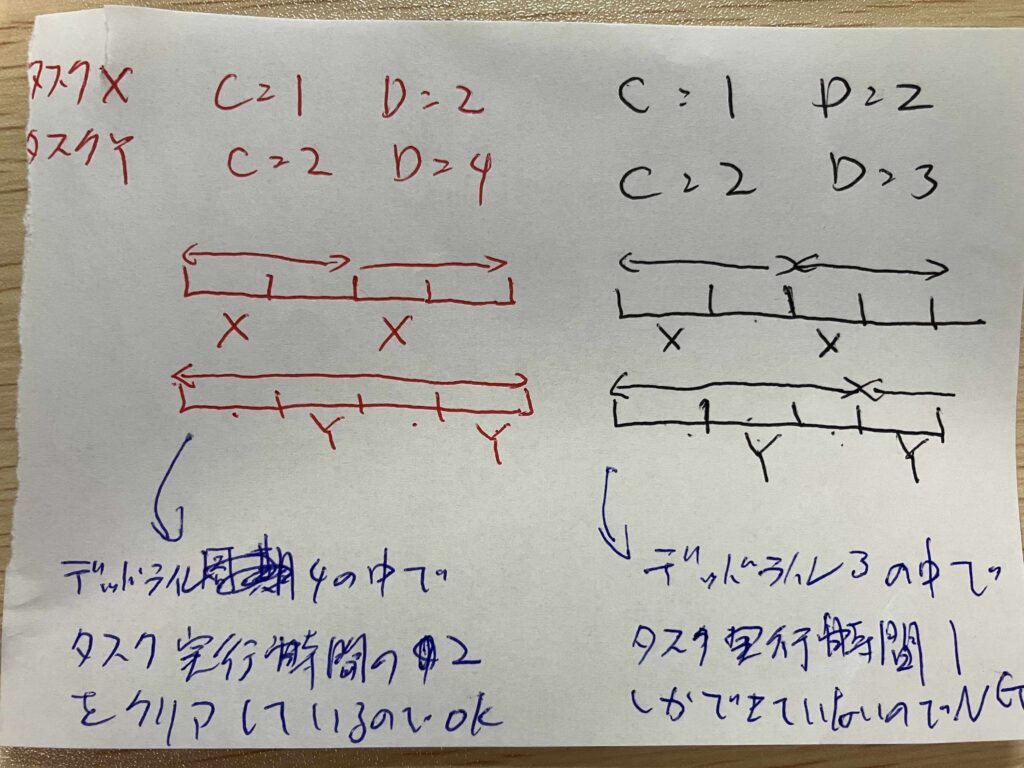

デッドラインスケジューリング

周期的なタスクのスケジューリングにおいて、タスクが必ずデッドラインを守る方式のこと。

複数の周期タスクがスケジュール可能となるためには、各タスクのC/Dを合計した値が1以下となる必要がある。

同期制御

セマフォ(semaphore)

semaphoreは「信号、シグナル」の意味

排他的な制御が必要な資源の管理に用いられる同期制御方式のこと。

タスクがある資源を使いたいとき、その資源のセマフォを獲得する(P操作)、資源の利用が完了すると解放する。(V操作)

一つの資源を多重に使用する場合、同一資源に対してP操作、V操作が連続して行われることがある。

P操作はセマフォ変数から1減算、V操作は1加算ということになる。P操作を行う時にセマフォ変数がゼロだと1減算できるまで待つことになる。すなわちセマフォ変数の初期値を1以上にすると、その初期値分の多重制御が可能となる。

優先度の逆転とデッドロック

優先度の逆転

セマフォによる資源の排他制御の結果、優先度の低いタスクが優先度の高いタスクより早く実行されてしまう現象を優先度の逆転(Priority Inversion)という。

優先度の低いタスクBが資源を獲得した後に、優先度の高いタスクAが同じ資源を使おうとすると、タスクBが資源を完了するまで待つことになり、優先度の低いBの方が優先して実行されてしまう。

ソフトウェアの開発

デバッグ

JTAG

シリアル通信でICの内部回路と通信する仕組み、基盤検査の標準規格(バウンダリスキャンテスト)

JTAG(Joint Test Action Group)という団体によって策定されたた規格のためこのように呼ばれる。

ICE(In-CirCuit Emulator)

MPUの機能をエミュレートし、デバッグ機能を備えたハードウェア、MPUに差し替えて利用する。

電子基盤や組み込みシステムを検査する試験装置のこと。

バウンダリスキャンテスト

ICの端子に埋め込まれた「テスト用回路」を使ってICの状態を調べたり、ICの端子が入出力する値を変更する技術

2つのIC間で端子同士が正常に配線されているか否かをテストするもので、断線だけでなく、ハンダ付け不良によるブリッジも検出できる。

ICが高集積化したことによってプローブが使えなくなったことからこのような機能をあらかじめカイロに組み込むようになった。

JTAG-ICE

ターゲットチップ上に搭載されているデバッグ用回路とエミュレータをJTAGで接続するデバッグ環境

ICEの簡易版として使われている。

バウンダリスキャンテストの標準方式

ビルドインセルフテスト

回路にテストパターン発生回路を含むもので、テストパターン発生部とテスト判定部がICチップニック見込まれている方式

逆に、チップにテストパターン発生回路などを組み込まないものをストアド方式と呼ぶ。

用語

ベクトルプロセッサ

多数のデータに同時に同じ演算を行うベクトル処理に適したプロセッサのこと。

1990年台までのスーパーコンピュータに多く用いられた設計

プロセッサ内部に大量に組み込まれたレジスタ(一時データ保存回路)および演算機によって一気に演算を実行することができる。

MPU(Micro Processor Unit)

パソコンの心臓部に使われるIC

Java EE(Java Platform,Enterprise Edition)

企業向けのアプリケーション開発ができる機能がセットになったプラットフォーム

構成要素としては、コンポーネント、コンテナ、コネクタの3つがある。

コンポーネントとはアプリケーションプログラムを構成する「部品」のようなもので、クライアント(Webブラウザ)の要求によって、サーバ上で動作するServletなどを含む。

Java Servlet:Webサーバー上で動くJavaで書かれたプログラムのこと

コンテナとは、コンポーネントの実行環境のこと。

コネクタとはデータベースや既存システムなどと、JavaEEのアプリケーションプログラムとの接続を実現するための(インタフェース)である。

EAI(Enterprise Application Integration)

直訳すると、企業のアプリケーション統合

異なる複数のシステム間のデータ連携をスムーズにする仕組み。

データスパイダーとか

UDDI(Universal Description, Discovery, and Integration)

インターネット上で提供されているWebサービスの情報を公開し、広く検索可能にするための仕組み。

SOAP(Simple Object Access Protocol)と呼ばれるXML、HTTPをベースとしたプロトコルによって実現されている。

エミュレータ

エミュレータはまねるの意味で、他のコンピュータ(実機)の模倣をするものである。

シミュレータ

シミュレータは現実の現象または、仮想の現象を模擬的に行う(シミュレート)するもので、シミュレーションモデルを用いたりする。

プロファイラ

プログラムを構成するモジュールや関数の実行回数、実行時間など、性能改善のための分析に役立つ情報を収集するツール

犯罪捜査において、情報を収集し分析することをプロファイリングというように、コンピュータソフトとしてのプロファイラも同様に、処理回数や処理時間に関する情報を集め、性能改善に役立てる。

SELinux(Security-Enhanced Linux)

直訳すると「セキュリティを強化したLinux」、スーパユーザによるリソースへのアクセスを制限して、侵入された際の影響を最小限に抑える。

Linuxのセキュリティを強化するためにNSA(米国国家安全保障局)によって開発された。

システムにアクセス可能なユーザーをより細かく制御することで不正アクセスに対する防御を強めている。

SELinuxの特徴として、通常のOSのスーパバイザ(root権限?)の権限を制御し、実行単位ごとにアクセス権を与える。

周波数

1秒間に繰り返す波の数のこと

1秒間に60回繰り返すなら周波数は60

周期

定期的に同じことが繰り返される事象において、一周して戻ってくるまでの時間

周波数の逆数となる。

1秒間に60回繰り返すなら周期は1/60

ESD(Electrostatic Discharge:静電気破壊)

静電気による機器の破壊

特に冬場は注意が必要

クロック発生器(クロックジェネレータ)

デジタルクロックと呼ばれる一定の周波数の信号を定常的に発生させる装置のこと。

電子機器にタイミングを伝える役目をしている。

電子機器の内部回路を正確に動作させるには一定の周波数の信号を送り続けることが必要となる。

Hz(ヘルツ)

周期的な減少の頻度を表す単位で、一秒当たりの正起回数(起きる回数)を示したもの。

分周

入力された周波数を(1/整数)倍することを言う。

例えば5分周の場合、5つの波を1つの大きな波に変換する。

エネルギーハーベスティング

別名「環境発電技術」とも言う。

周りの環境から微小なエネルギーを収穫(ハーベスト)して、電力に変換する技術のこと。

太陽光発電、風力発電など

熱電変換素子

熱エネルギーを電気エネルギーに直接変換する素子のこと。

金属(半導体)の温度差が電力(熱起電力)に直接変換されるゼーベック効果を利用している。

ちなみに、電圧が温度差に変換される現象をペルチエ効果といい、ポータブル冷蔵庫やCPUの冷却で実用化されている。

光起電力効果

光の照射によって物体中に起電力が発生する現象

ソーラーパネルなどで利用される。

焦電効果

赤外線エネルギーによって素子に温度差を与え、素子の表面に電荷が生じる現象を焦電効果といいい、赤外線センサとして利用されている。

ピエゾ効果

電圧効果ともいい、圧力を加えると電荷ができる現象で、ライター、ガスコンロの点火などに利用されている。

最近では発電床に応用され、LEDと組み合わせて停電時の誘導灯として利用されている。

フールプルーフ

人がミスをしようとしてもできないようにすること。

フールは愚者、プルーフは耐えると言う意味

誤入力が発生しても、プログラムやシステムを以上終了させずに、エラーメッセージを表示して次の操作を促すような設計

フォールトトレランス

システムの構成要素に故障(フォールト)が発生しても全体としては正しく動作するようにした設計、もしくはそのようなシステムの性質のこと。

構成要素を二重化したり、システムの動作を停止しないで故障した部品の修理交換ができるようにする。

JIS X 25010:2013

機能適合性

明示された状況下で使用するとき、明示的ニーズ及び暗黙のニーズを満足させる機能を、製品またはシステムが提供する度合い

性能効率性

明記された状態(条件)で使用する資源の量に関する性能の度合い

互換性

使用性

信頼性

明示された時間帯で、明示された条件下に、システム、製品または構成要素が明示された機能を実行する度合い

セキュリティ

保守性

意図した保守者によって、製品またはシステムが修正することができる有効性及び効率性の度合い

移植性

イベントシステム

キーボード、マウス、タッチなどでアプリケーション内のオブジェクトにイベントを送信する方法

マイクロカーネル

OSの中核部であるカーネルの設計様式の一つで、カーネル自体には最低限の機能しか実装せず、OSの多くの機能をモジュールとして独立させたもの。

インタフェース

コンピュータにおいてはAの回路(装置)とBの回路(装置)の間に設置し、動作させるのに必要な条件をマッチングさせるもの。

MVC(Model View Controller)

ヒューマンインタフェースを持つシステムにおいて、機能とヒューマンインタフェースの依存を弱めることによって、修正性や再利用性を向上させることを目的としたアーキテクチャパターン

Model:アプリケーションのデータと手続き部分(ビジネスロジック)である。データの変更をビューに通知する。

View:モデルのデータを取り出してユーザーが見るのに適した形で表示する。

Controller:UIからの入力を担当する部分

C1カバレージ

プログラムの分岐網羅率

C1が分岐網羅、カバレージが網羅率(coverge)のこと。

カバレージにはC0、C1、C2の3種類がある。

- C0:命令分岐網羅、全体のどの程度の命令を網羅したか

- C1:分岐網羅、命令の分岐結果をどの程度網羅したか

- C2:条件網羅、分岐命令における条件のパターン数のうちどの程度網羅したか

C2は全ての可能な結果を少なくとも1回検証すれば良く、C2カバレッジが100%になっても、C0とC1が100%になるとは限らない。

DC電源

DCとは「Direct Current:直流」の意味

時間と共に流れる極性、大きさが変わらない電流をDCと呼ぶ

AC電源

ACとは「Alternating Current:交流」の意味

時間と共にその大きさと極性が周期的に変化する電流のこと。

一般家庭のコンセントでは、東日本では50Hz(1秒間に50回振動)、西日本では60Hzとなっている。

スマートグリッド

次世代電送網のこと、電力の流れを需要側、供給側の両方から制御し最適化できる送電網

スマートは賢いの意味

RAM、ROM

RAM(Random Access Memory)はCPUが作業用に使うメモリのこと。

ROM(Read Only Memory)は読み出し専用で書き込みができないメモリのこと。

DMA(Direct Memory Access)

CPUを介さずにメインメモリと周辺デバイスとの間でデータを送受信するための仕組み

方向レジスタ、データレジスタ

方向レジスタは端子の方向(入力、出力)を決定するレジスタ

データレジスタはデータを格納するレジスタ

シリアル通信

データを送受信するための伝送路を1本または2本使用して、データを1ビットずつ連続的に送受信する通信方式

シリアルの意味は直列

ATPG(Automatic Test Pattern Generation)

論理回路情報からLSIテストのための入力パターンを自動生成すること。

テストパターンを自動生成するツールをATPGツールと呼ぶ

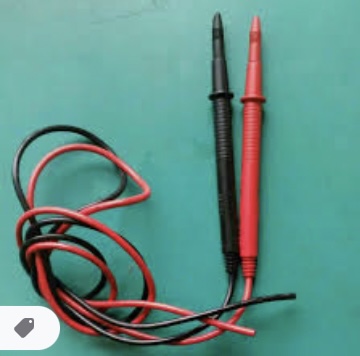

テストプローブ

回路上の導通試験を行う、ハードウェア上の配線に断線があるか否かを見つけるのに重要

LSB(Least Significant Bit)、MSB(Most Significant Bit)

ビット列があったときに一番右にあるのが、LSB、一番左にあるのがMSB

スレッドとプロセス

プロセスは1つのプログラムの実行環境、1つのプロセスには1つのアドレス空間(メモリ空間)が割り当てられる。

スレッドはプロセス内で並列動作する実行単位で、CPUコアを利用する単位

同一プロセス内のスレッドはアドレス(メモリ)空間を共有する。

CPU資源(PSW:プログラムカウンタ、ステータスレジスタ)とレジスタはスレッドごとに割り当てられる。

スレッド間通信は同一空間の(共有)メモリなどを用いて、アドレス空間の切替えなしで行われるのに対して、プロセス間通信はアドレス空間の切替えなどのオーバーヘッドが大きい。

コンテキスト

プロセスあるいはスレッドの実行状態値のことで、PSW、レジスタ、スタックポインタ、ページ変換テーブルの値などの情報である。

同一アドレス空間のスレッドとプロセスの間でコンテキストの切替はないが、違うアドレス空間のスレッドとは、アドレス空間の切替が必要となり、コンテキストの切り替えは高速には行われない。

割り込みと、ポーリング

割り込みはハードウェアで外部の状態が変わっていないかを判断して、変わったら即座にCPUに割り込み信号を伝達する方式

ポーリングはソフトウェアが外部の状態が変わっていないか周期的にチェックをする。CPUのポートに状態の変化が知らされた後に定期的にチェックして状態が変わったかを判断する。

ポーリングは即座に反応できないという問題があるが、ソフトウェアだけで実装できるというメリットもある。

トランジスタ

電気の流れを制御する電子部品、信号を増幅したり、信号によって回路のON/OFFを制御したりする。

NPN型のトランジスタではベースからエミッタに少しの電流を流せば、コレクタからエミッタに増幅した電流が流れる。

コンデンサ

受け取った電力を消費したり、貯めたり、放出したりする電子部品

2枚の金属板で絶縁体を挟み込む形で構成される。電力を流すと(絶縁体があるため)電気は流れず、金属板に+、ーそれぞれの電化が蓄積することになり、電気が蓄えられる。

暗号化方式

AES(Advanced Encryption Standard)

DES(Data Encryption Standard)の後継の共通鍵暗号方式である。

鍵長を128、198、256ビットの3種類から選べる。

ElGamal(エルガマル)暗号

離散対数問題を応用した公開鍵暗号方式

RSA

大きな整数の素因数分解の困難性を応用した公開鍵暗号方式

開発者3名の頭文字から命名されている。

楕円曲線暗号

楕円曲線状の離散対数問題を応用した公開鍵暗号方式

MISRA-C

ソフトウェアに基づいて制御する乗り物に対してC言語を使うガイドラインのこと

MISRA(Motor Industry Software Reliability Association)はミスラと読み、自動車産業界におけるソフトウェアの信頼性を高くすることを目的とした協会のこと

MISRAを直訳すると「自動車産業ソフトウェア信頼性協会」

Objective-C

オブジェクト指向の機能を持つ、C言語の上位互換言語

スマートフォンの開発などに利用されている。

C99

ISOで定められたC言語の規格

正式名称は(ISO/IEC 9899:1999)

可変長配列、複素数型などをサポートする。

System C

システム設計を行うためのC言語でC++のクラスライブラリとして提供されている。

加速時の距離を求める公式

\(x = v_0t+\frac{1}{2}at^2\)

パワーゲーティング

ゲーティングとは門の開閉のことであり、パワーゲーティングとは電源を遮断して電力供給量を制限するものである。

プロセッサをいくつかのブロックに分割し、動作させる必要のないブロックへの電源供給を止めることによって省電力化を図る。

クロックゲーティング

動作していない回路ブロックへのクロック供給を遮断し、省電力化を図る。

ターボブーストテクノロジ

マルチコアプロセッサにおいて、使用しないコアの消費電力枠を動作しているコアに割り当てて処理の高速化を図る。

IntelのCore iシリーズに搭載されている。

コンパイラ最適化

コード効率から見た最適化

定数の畳み込み

コンパイル時に確定している定数をあらかじめ計算してしまう。

実行速度の向上から見た最適化

関数インライン展開

関数呼び出しのオーバーヘッドを省略することで高速化を図る、一般にコード量は増える。

ループ内の不変式の移動

ループ何の不必要な処理を外に追い出すこと。高速化できるが、コード量は同じ

ループのアンローリング

ループ変数処理のオーバーヘッドを減らすと共にパイプラインの乱れを防ぐ、高速化できるが一般にコード量は増える。

SoC(System on a Chip)

ScCは1チップにさまざまな機能を持った回路を集積し、1つのシステムとして動作するように設計された集積回路の総称

ワンチップで実現しているので、小型で低消費電力のシステムを開発することが可能

スマートフォンを代表とする携帯端末などで広く利用されている。

IPコア

ScCの構成要素であり、半導体を構成する再利用可能な回路コンポーネントの設計情報

IPコアは汎用性、再利用性を考慮して設計され、完成された部品として提供されるため利用者はその機能を1から設計する必要がなく、開発期間を短縮できる。

ソフトウェア開発でいう「ライブラリ」の、回路バージョン

IPコアの代表例としては、デジタルカメラに搭載される画像や音声データの圧縮、復号器などがある。

WebDAV

Webサーバにある利用者のリソースに、他のサーバが利用者に代わってアクセスすることを許可するための認証プロトコル

Webサーバ上のファイル編集をFTPなどを使わずHTTPだけで編集、取得できる。

スタックフレーム

C言語のプログラムにおいて、関数を使用するときにスタック上に積み上げられたデータをまとめたもの。

各関数が呼び出されると積み上がる(PUSH)もので、終了すればスタックから取り除かれる。(POPされる)

プログラム全体のスタックフレームのサイズが確保したサイズ内に収まっているかを確認するには、各関数が使用するスタックフレームサイズと各関数の呼び出し関係(呼び出しツリー)が必要

インサーキットエミュレータ

CPUの代わりに回路上に接続され、CPUをエミュレートする装置のこと。

実際のプロセッサの動作を忠実に再現するが、最近では複雑化したCPUに開発が追いつかなくなっている。

仮装デバイスドライバ

複数のアプリケーションから同一のハードウェアにアクセする場合、デバイスを仮装化し、破綻なく生業できるよう調停する役割を持ったデバイスドライバ

あるアプリケーションなどがハードウェアを占有しようとすると、仮装デバイスドライバがその命令を奪い返して、複数の命令が重なっても不都合なく実行できるようにする。

ファジングテスト(fuzzing)

テスト対象に問題を引き起こす可能性があるデータを大量に送り込み、その応答や挙動を監視することによって脆弱性を検出する。

英語のfuzzはふわふわしたわたげのことで、予測不能な入力データ(ふわふわしたデータ)を入れるイメージ

状態遷移テスト

テスト対象の振る舞いを状態遷移表で整理し、発生し得る遷移をテストする手法

システムによっては、同じ入力条件であっても動作中の状態によって異なる制御や出力を行う仕様の場合があり、そのような状態の変化を網羅的に設定しテストを行う手法

特許の専用実施権

特許の専用実施権とは、特許を独占的・排他的に実施できる権利である。

A社が保有する特許の専用実施権をB社に与えた場合、他の第三者に特許を許諾できないばかりでなく、A社ですらその特許を実施することはできなくなる。

複数の実施社に同一範囲の特許の実施を許諾する場合は、通常実施権を設定する。

2の補数で負の数を表す

2の補数を用いて負の数を表現することができる。

2の補数とは、2進数において全ビットを反転させて「1」を加えたもの。

例えば45(101101)の負の数、-45を2の補数で表すと(010011)となる。このつの2進数を足すと100000となり桁上がりがありその下のビットは全て0となる。

コンピュータが計算しやすいようにこのようなルールで負の数を表す。

Ah(アンペアアワー)

A(アンペア)は電流の単位、Ahは電流の容量を表す単位

10Ahは電流10Aを1時間流す能力があるということ

リエントラント(再入可能)

実行中のプログラムが同時に他のプログラムから呼ばれた場合も正常に処理できる性質のこと。

使用するデータを共有しないよう設計しているため、呼び出し元のプログラムのデータ同士が干渉することなく実行できる。

チップセレクト信号

チップセレクト信号はROMのどのメモリに対する接続かを識別する信号

16ビットのうち上位2ビットをチップセレクト信号とした場合、負論理であれば、01、10、11の時にLowとなりセレクトされる。

アクセスできるメモリアドレスの範囲は0100 0000 0000 0000(4000)〜 1111 1111 1111 1111(FFFF)となる。

限界値分析、同値分析

テストデータの取り得る範囲の中から、同じ処理結果となる範囲を一つのクラスとし、いくつかのクラスに分割する。また、正常な処理が行われる値の範囲を「有効同値クラス」エラー処理となる値の範囲を「無効同値クラス」と呼ぶ。分割後の各クラスの代表的な値をテストデータとする方法が「同値分割」である。さらに、同値分割で分割されたクラスの境界(限界)値をテストデータとするのが「限界値分析」である。